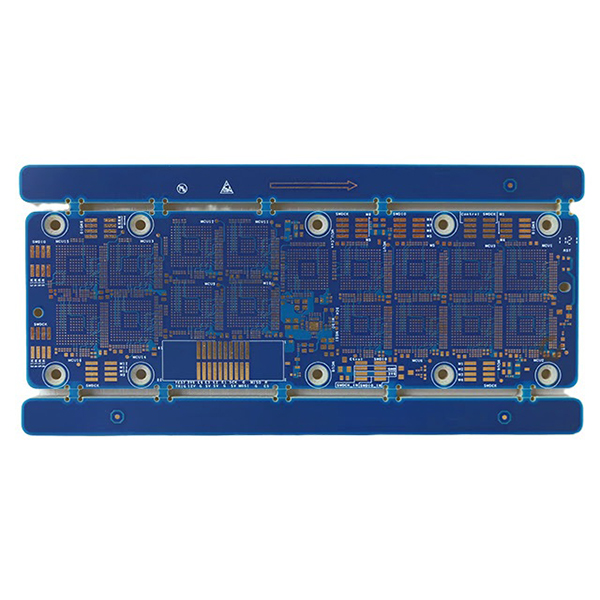

14-warstwowa, 3-etapowa produkcja półprzewodnikowych płytek testowych PCB

14-warstwowa, 3-etapowa produkcja półprzewodnikowych płytek testowych PCB jest jednym z podstawowych procesów w dziedzinie testowania chipów półprzewodnikowych, zapewniając wysoką wydajność sprzętu do testów funkcji chipów i weryfikacji niezawodności.

Opis

14-warstwowa, 3-etapowa produkcja półprzewodnikowych płytek testowych PCB

14-warstwowa, 3-etapowa produkcja półprzewodnikowych płytek testowych PCB, o wysokiej gęstości, wysokiej precyzji i wysokiej niezawodności, jest szeroko stosowana w różnych zaawansowanych urządzeniach do testowania półprzewodników i służy jako kluczowa podstawa do zapewnienia jakości i wydajności chipów.

Główne cechy 14-warstwowej, 3-etapowej produkcji półprzewodnikowych płytek testowych PCB

- Wielowarstwowe połączenia o wysokiej gęstości:14-warstwowa struktura w połączeniu z 3-etapową technologią HDI obsługuje złożone układy obwodów i izolację wielu sygnałów, spełniając wymagania dotyczące wysokiej gęstości i szybkiej transmisji sygnału.

- Precyzyjny proces produkcji:Wykorzystuje wysokiej klasy materiał Shengyi S1000-2M, z pozłacaną powierzchnią, minimalną średnicą otworu 0,5 mm i minimalnym śladem / przestrzenią 4/4 mil, odpowiedni do precyzyjnych testów.

- Wysoka niezawodność i integralność sygnału:Zaawansowana technologia „buried/blind via” i połączenia międzywarstwowe znacznie zwiększają integralność sygnału i zdolność przeciwdziałania zakłóceniom, zapewniając dokładne dane testowe.

- Doskonałe materiały i wykonanie:Wysoka odporność na temperaturę i korozję, odpowiednia do długotrwałych i złożonych środowisk testowych.

- Elastyczna konstrukcja i personalizacja:Obsługuje różne interfejsy testowe i niestandardowe projekty, ułatwiając integrację z różnymi systemami testowymi.

Wprowadzenie do 14-warstwowej, 3-stopniowej półprzewodnikowej płytki testowej

- 14 warstw:Odnosi się do 14 warstw przewodzących wewnątrz płytki PCB, umożliwiając złożone połączenia obwodów i izolację sygnału poprzez wielowarstwowe układanie, odpowiednie dla wymagań sygnału o dużej gęstości i dużej prędkości oraz promujące integralność sygnału i kompatybilność elektromagnetyczną.

- 3 kroki:Zwykle odnosi się do „kroków” w technologii HDI (High Density Interconnect) – trzech procesów wiercenia laserowego i trzech procesów laminowania, wspierających drobniejsze zakopane / ślepe struktury przelotowe dla bardziej elastycznych połączeń i większej gęstości, odpowiednich do zastosowań o dużej prędkości / wysokiej częstotliwości.

- Półprzewodnikowa płytka testowa:Specjalnie używana do funkcji takich jak testowanie funkcji chipa i testowanie starzenia, wymagająca wysokiej niezawodności, wysokiej precyzji i doskonałej zdolności transmisji sygnału.

Główne zastosowania

- Systemy testowania półprzewodników, takie jak urządzenia do obsługi testów chipów, automatyczne urządzenia testujące ATE, karty sond i płyty obciążeniowe.

- Scenariusze testowe o wysokim zapotrzebowaniu, takie jak testowanie funkcji układu scalonego, testowanie starzenia i analiza awarii.

- Nadaje się do pakowania i testowania półprzewodników oraz badań i rozwoju z wymaganiami dotyczącymi wysokiej częstotliwości, dużej prędkości, wysokiej precyzji i wysokiej niezawodności.

English

English  Français

Français  Tiếng Việt

Tiếng Việt  Italiano

Italiano  Nederlands

Nederlands  Türkçe

Türkçe  Svenska

Svenska  Polski

Polski  Română

Română  Latviešu

Latviešu  한국어

한국어  Русский

Русский  Español

Español  Deutsch

Deutsch  Українська

Українська  Português

Português  العربية

العربية  Indonesian

Indonesian  Čeština

Čeština  Suomi

Suomi  Eesti

Eesti  Български

Български  Dansk

Dansk  Lietuvių

Lietuvių  Bokmål

Bokmål  Slovenčina

Slovenčina  Slovenščina

Slovenščina  Ελληνικά

Ελληνικά  Magyar

Magyar  עברית

עברית